آموزش نرم افزار Modelism و نکات کاربردی که باید بدانید

Modelsim برنامه ای است که توسط Mentor Graphics برای شبیه سازی طرح های VHDL و Verilog ساخته شده است. این برنامه پرکاربردترین برنامه شبیه سازی در تجارت و آموزش است. این مقاله اول برای تان باز می کند که شبیه سازی چه اهمیتی دارد و به بعد این که چه طور می توانید از Modelsim Student Edition برای استفاده شخصی تان بهره ببرید، می پردازد.

شبیه سازی یک مرحله حیاتی در طراحی FPGA و ASIC است. شبیه سازی به طراح این امکان را می دهد که به طرحش پر و بال دهد و ببیند کدی که نوشته است؛ چه طور به محرک واکنش نشان می دهد. در یک شبیه سازی کامل تمام حالت های ممکن طراحی پیاده سازی می شود تا این اطمینان به وجود بیاید که به تمام ورودی ها به درستی پرداخته می شود. خطا های مختلفی هستند که اگر طراحی تان را شبیه سازی نکنید، خیلی راحت ممکن است مرتکب شان شوید، مثال بارزِ یکی از آن ها جا گذاشتن عبارت if است. خب پس بهتر است وقت را تلف نکنیم و نصب و راه اندازی مدلیسم را شروع کنیم!

Modelsim را با پارامتر های پیش فرض نصب کنید. توجه داشته باشید که باید از منتور گرافیک مجوز بگیرید. در پایان نصب هم باید گزینه Finish را انتخاب کنید، یک پنجره مرورگر با فرم License Request باز می شود. یادتان باشد که با کلیک کردن روی لینک درخواست مجوز موجود در Bookmark مرورگرتان یا لینک ارسال شده در وب جوابی نخواهید گرفت.

کدی که شبیه سازی خواهیم کرد، طرح VHDL زیر است. کد فعلی اهمیتی ندارد، بنابراین اگر در حال یادگیری Verilog هستید ، نگران نباشید! برای این آموزش نیازی به دانستن VHDL نیست. کد VHDL یک And Gate ساده درست می کند و برخی از ورودی ها را از طریق یک محیط تست می گیرد. کد زیر موجود در and_gate.vhd و testbench را در and_gate_tb.vhd کپی کنید.

and_gate.vhd:

library ieee;

use ieee.std_logic_1164.all;

entity and_gate is

port (

input_1 : in std_logic;

input_2 : in std_logic;

and_result : out std_logic

);

end and_gate;

architecture rtl of and_gate is

signal and_gate : std_logic;

begin

and_gate <= input_1 and input_2;

and_result <= and_gate;

end rtl;

and_gate_tb.vhd:

library ieee;

use ieee.std_logic_1164.all;

entity and_gate_tb is

end and_gate_tb;

architecture behave of and_gate_tb is

signal r_SIG1 : std_logic := ‘0’;

signal r_SIG2 : std_logic := ‘0’;

signal w_RESULT : std_logic;

component and_gate is

port (

input_1 : in std_logic;

input_2 : in std_logic;

and_result : out std_logic);

end component and_gate;

begin

and_gate_INST : and_gate

port map (

input_1 => r_SIG1,

input_2 => r_SIG2,

and_result => w_RESULT

);

process is

begin

r_SIG1 <= ‘0’;

r_SIG2 <= ‘0’;

wait for 10 ns;

r_SIG1 <= ‘0’;

r_SIG2 <= ‘1’;

wait for 10 ns;

r_SIG1 <= ‘1’;

r_SIG2 <= ‘0’;

wait for 10 ns;

r_SIG1 <= ‘1’;

r_SIG2 <= ‘1’;

wait for 10 ns;

end process;

end behave;

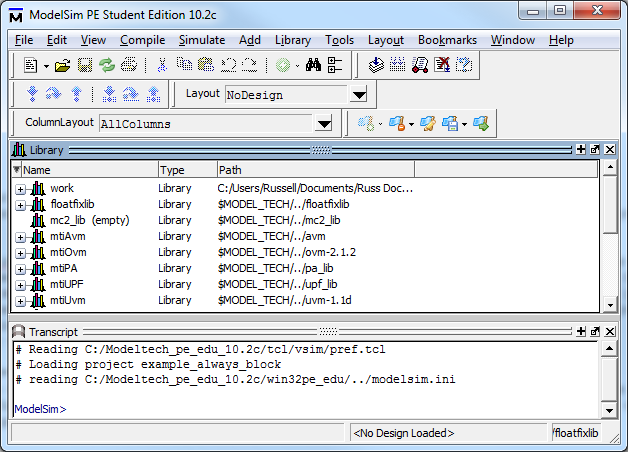

بیایید Modelsim را باز کنیم . با پنجره ای به این شکل رو به رو خواهید شد:

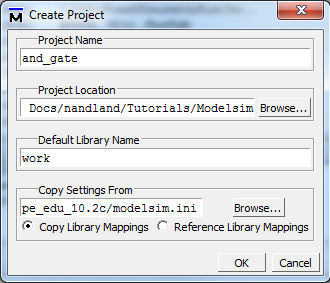

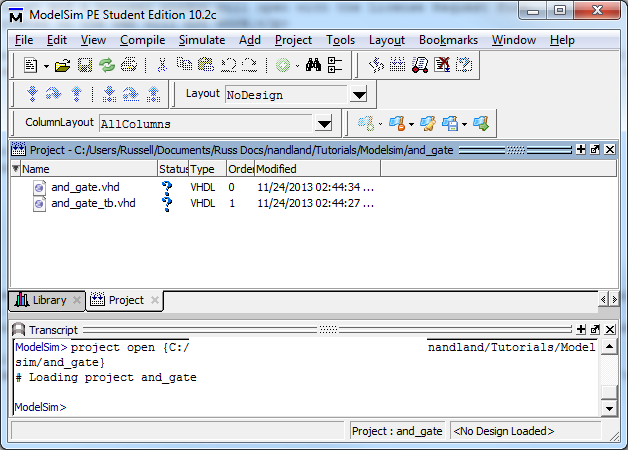

برای شبیه سازی، باید یک پروژه ایجاد کنید. روی File > New > Project کلیک کنید. پنجره ای را در سمت چپ مشاهده خواهید کرد. یک مکان برای پروژه جدیدتان انتخاب کنید و نامش را and_gate تایپ کنید . پروژه ها در Modelsim پسوند فایل .prj دارند. سایر تنظیمات را بگذارید در حالت پیش فرض شان باشند. گزینه Default Library Name می گوید که همه کد ها در کتابخانه Work کامپایل می شوند.

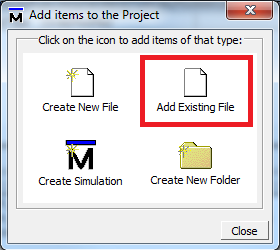

روی Add Existing File کلیک کنید. به مکانی که and_gate.vhd و and_gate_tb.vhd را دانلود کرده اید؛ بروید و هر دو را به پروژه تان اضافه کنید . سایر تنظیمات را در حالت پیش فرض شان رها کنید. بعد از اتمام کار، روی گزینه OK کلیک کنید.

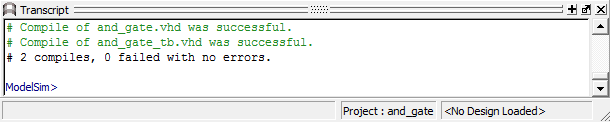

حالا اگر دقت کنید می بینید که فایل ها با موفقیت به پروژه تان اضافه شده اند. آن دو علامت سوال آبی را در شکل پنجره پروژه Modelsim در بالا می بینید ؟ این یعنی Modelsim هنوز فایل ها را کامپایل نکرده است. شما باید فایل های منبع را کامپایل کنید. برای این کار بر روی and_gate.vhd راست کلیک کنید، روی گزینه Compile و بعد روی Compile All کلیک کنید. همان طور که در تصویر زیر نشان داده شده است، باید پیام ها در پنجره کنسول به رنگ سبز در بیایند. این یعنی کامپایل موفقیت آمیز بوده است.

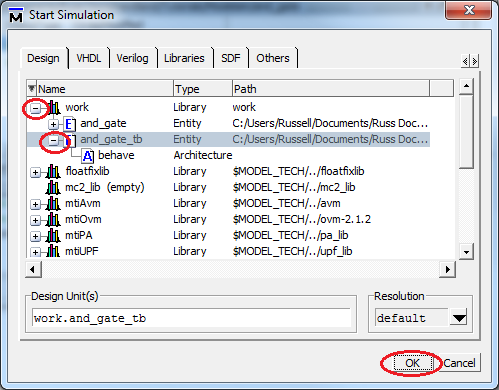

روی Simulate در نوار منو کلیک کنید، بعد روی Start Simulation کلیک کنید. با این کار پنجره Start Simulation باز می شود . روی علامت مثبت در کنار work کلیک کنید، بعد روی علامت مثبت در کنار and_gate_tb کلیک کنید. مطمئن شوید که and_gate_tb و نه and_gate را انتخاب کرده اید؛ زیرا می خواهیم طرح را در محیط تست شبیه سازی کنیم. هنگامی که and_gate_tb برجسته شد، روی OK کلیک کنید.

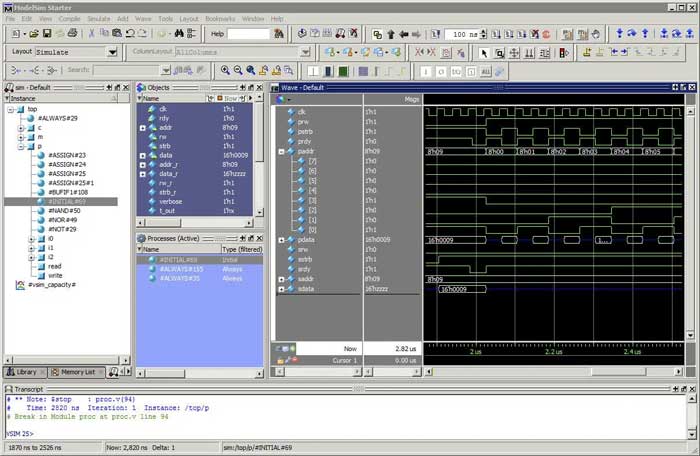

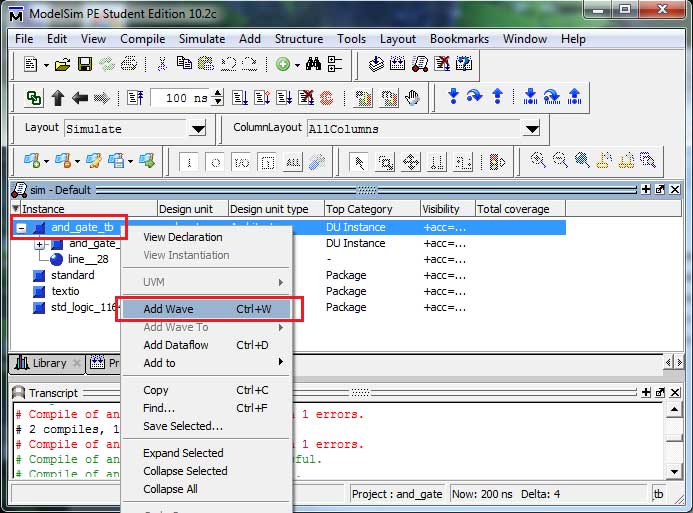

تقریبا تمام شد! حالا همه چیز برای شبیه سازی آماده است. حالا بیشتر زمانی که از Modelsim استفاده میکنید، صرف مشاهده شکل موج می شود. نمای شکل موج شامل امواج (0 و 1 باینری ، ارقام هگزا دسیمال، ارقام باینری ، انواع داده شمارشی و غیره ) برای همه سیگنال های طرح تان است. این موج نشان می دهد که ماژول شما چه طور به محرک های مختلف واکنش نشان می دهد. شکل بعدی به شما نشان می دهد که نمای شکل موج شما چه طور به نظر می رسد، البته اول باید چند سیگنال برای نظارت اضافه کنید. در این مثال، ما تمام سیگنال های موجود در محیط تست را بررسی می کنیم . برای این کار روی and_gate_tb در پنجره Sim در سمت راست و روی Add Wave کلیک کنید. همچنین می توانید روی سیگنال ها کلیک کنید و آن ها را از پنجره های دیگر Modelsim به پنجره موج Drag کنید.

در کنار این مطلب دانلود کنید: آموزش صفر تا صد مهندسی نرم افزار

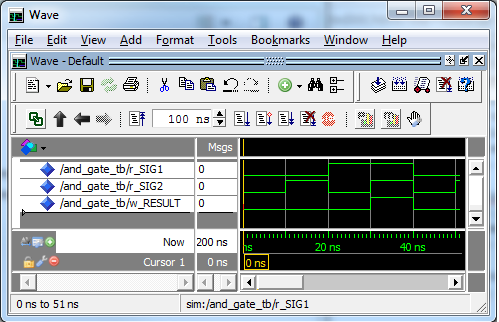

اینجا پنجره شکل موج شما است. همه سیگنال های موجود در محیط تست به عنوان سیگنال هایی که می توانید بر آن ها نظارت کنید، اضافه شده اند. برای راه اندازی عملیات شبیه سازی ، روی نماد یک تکه کاغذی که کنارش یک فلش رو به پایین دارد و در کنار فیلد 100 ns قرار گرفته کلیک کنید. با این کلیک ، شبیه سازی شما به مدت 100 نانوثانیه اجرا می شود. می بینید چه طور سیگنال ها تغییر می کنند! تبریک می گویم ! شما اولین شبیه سازی Modelsim تان را انجام دادید!

یک یاداوری و چند نکته مهم تکمیلی

اگر تا اینجای کار با ما پیش اماده باشید متوجه شده اید که

ModelSim یک شبیهساز قدرتمند برای طراحی و تحلیل مدارهای دیجیتال است که از زبانهای توصیف سختافزار مانند VHDL، Verilog و SystemVerilog پشتیبانی میکند. این نرمافزار توسط شرکت Mentor Graphics (اکنون تحت مالکیت Siemens) توسعه داده شده و بهطور گسترده در طراحی تراشهها و سیستمهای دیجیتال مورد استفاده قرار میگیرد.

1. معرفی نرمافزار ModelSim

کاربردهای اصلی:

- شبیهسازی (Simulation): بررسی رفتار مدارهای دیجیتال.

- تست و اعتبارسنجی: اطمینان از صحت عملکرد کدهای طراحیشده.

- خطایابی (Debugging): شناسایی و رفع خطاهای منطقی یا طراحی.

- آنالیز زمانبندی: بررسی سیگنالهای ورودی و خروجی.

2. نصب و راهاندازی

مراحل نصب:

- نسخه نرمافزار ModelSim را از سایت رسمی یا منابع معتبر دانلود کنید.

- در طول نصب، مسیر نصب را مشخص کنید.

- در صورت نیاز، لایسنس را فعال کنید:

- برای نسخههای دانشجویی، از ModelSim PE Student Edition استفاده کنید.

- نسخههای حرفهای به لایسنس تجاری نیاز دارند.

3. مفاهیم اولیه

زبانهای پشتیبانیشده:

- VHDL: زبان توصیف سختافزار سطح بالا.

- Verilog: زبان پرکاربرد برای طراحی دیجیتال.

- SystemVerilog: نسخه پیشرفته Verilog با قابلیتهای بیشتر.

واحدهای اصلی:

- Entity/Module: نشاندهنده یک بخش از سیستم دیجیتال.

- Signal/Variable: سیگنالها برای انتقال داده بین بخشهای مختلف مدار.

- Testbench: کدی برای شبیهسازی رفتار مدار در شرایط مختلف.

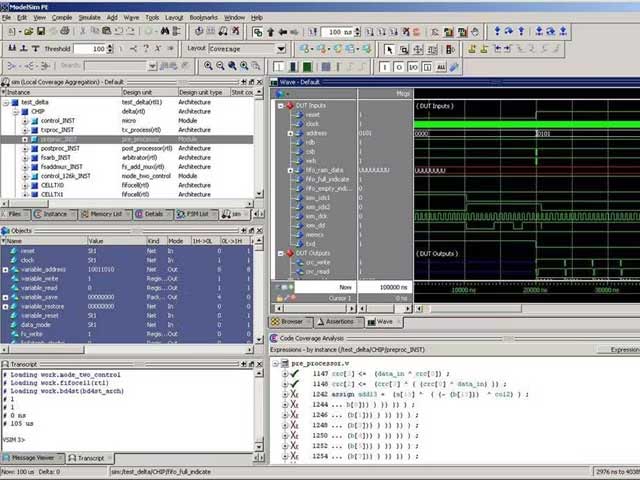

4. محیط کار ModelSim

بخشهای اصلی رابط کاربری:

- Library Window: نمایش کتابخانهها و فایلهای پروژه.

- Transcript Window: نمایش پیامهای سیستم، خطاها، و دستورات واردشده.

- Waveform Window: نمایش سیگنالها بهصورت نمودار زمانی.

- Source Window: ویرایشگر کد برای نوشتن و مشاهده کدها.

5. شروع کار با ModelSim

1. ایجاد یک پروژه جدید

- از منوی File > New > Project گزینه New Project را انتخاب کنید.

- نام پروژه و مسیر ذخیرهسازی را وارد کنید.

- نوع پروژه را مشخص کنید: VHDL، Verilog یا Mixed Language.

2. افزودن فایلها

- از طریق گزینه Add Existing File میتوانید فایلهای موجود را به پروژه اضافه کنید.

- برای ایجاد فایل جدید، از گزینه Create New File استفاده کنید و زبان موردنظر (مثلاً VHDL یا Verilog) را انتخاب کنید.

3. نوشتن کد

یک کد ساده برای یک مدار AND در Verilog:

4. ایجاد تستبنج (Testbench)

برای تست مدار، تستبنج زیر را بنویسید:

5. کامپایل کردن کد

- در پنجره Transcript، دستور زیر را برای کامپایل فایلها وارد کنید:

6. اجرای شبیهسازی

- برای اجرای شبیهسازی، دستور زیر را وارد کنید:

- سپس، پنجره شبیهسازی باز میشود و نتایج را مشاهده خواهید کرد.

7. نمایش سیگنالها در Waveform

- در پنجره شبیهسازی، از منوی Add > To Wave > Signals in Design سیگنالها را به پنجره Waveform اضافه کنید.

- دکمه Run را بزنید تا سیگنالها نمایش داده شوند.

این نکات و ترفندهای کاربردی رو بلد باشید

1. استفاده از دستورات شبیهسازی

- monitor$: برای نمایش مقادیر سیگنالها.

- display$: مشابه monitor اما فقط یکبار اجرا میشود.

- stop$: توقف شبیهسازی.

- finish$: پایان شبیهسازی.

2. تنظیم زمان شبیهسازی

- از دستور زیر برای تنظیم مدتزمان اجرا استفاده کنید:

3. اشکالزدایی کد

- از پیامهای خطای Transcript برای رفع مشکلات استفاده کنید.

- برای بررسی رفتار سیگنالها، سیگنالهای مشکوک را به پنجره Waveform اضافه کنید.

4. ذخیره و بازیابی Waveform

- برای ذخیره نتایج شبیهسازی، از گزینه File > Save در پنجره Waveform استفاده کنید.

دانلود رایگان: آموزش همه زبانهای برنامه نویسی رایج

واقعا مفید و با جزییات توضیح دادهاید ممنون

پاسخ